模擬集成電路設計全攻略 從理論到流片的深度實踐

模擬集成電路是連接現實世界與數字系統的橋梁,其設計融合了物理直覺、數學建模與工藝實踐的獨特藝術。本文將為您系統解析模擬集成電路設計的核心流程、關鍵技術及實戰策略,提供一份從入門到精通的全面攻略。

一、 設計起點:需求分析與規格定義

成功的模擬IC設計始于清晰、量化的規格定義。設計者需與系統工程師緊密協作,將系統級需求(如信號帶寬、動態范圍、噪聲容限、功耗預算、電源電壓、溫度范圍等)轉化為晶體管級的電路指標(如增益、帶寬、相位裕度、壓擺率、失調電壓、共模抑制比等)。此階段建立的設計規格書是后續所有工作的基石,也是最終流片驗收的標尺。

二、 核心架構:電路拓撲選擇與建模

根據規格要求,選擇合適的電路架構是設計的關鍵一步。

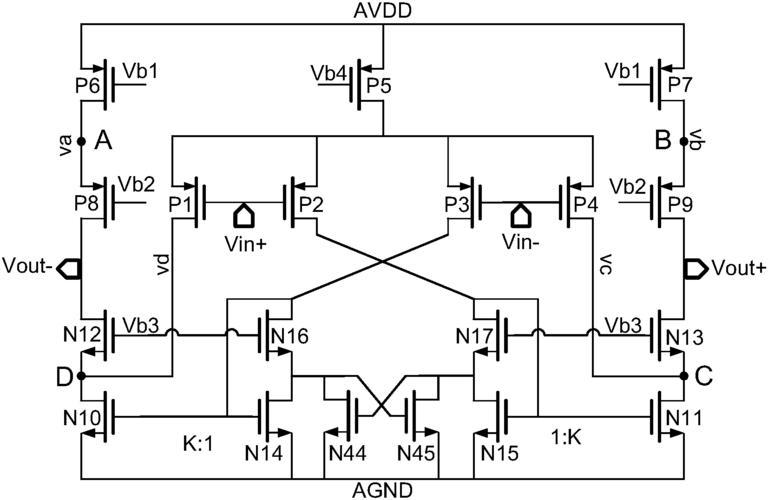

1. 放大器家族:從經典的共源共柵、折疊共源共柵到兩級運放、軌到軌輸入/輸出結構,需在增益、速度、功耗、面積和輸出擺幅之間權衡。

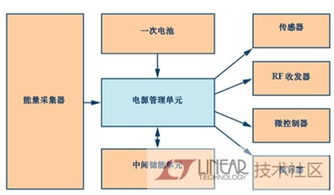

2. 基準源與偏置電路:帶隙基準是模擬電路的“心臟”,提供與電源電壓、工藝及溫度(PVT)變化無關的穩定電壓/電流。低壓、高階曲率補償等先進技術是高性能設計的必備。

3. 數據轉換接口:模數轉換器(ADC)與數模轉換器(DAC)架構繁多(如逐次逼近型SAR、流水線型、Sigma-Delta型),選擇取決于分辨率、速度、功耗及面積約束。

此階段需借助SPICE或Verilog-A等工具進行行為級或晶體管級建模與仿真,快速驗證架構可行性。

三、 晶體管級實現:設計與仿真迭代

這是設計的核心執行階段,將架構轉化為具體的版圖前電路。

- 器件尺寸確定:基于工藝庫模型(如BSIM),通過手工計算(gm/Id方法等)或優化工具,確定每個MOS管的寬長比(W/L)、偏置點,以滿足增益、帶寬、噪聲等指標。深入理解短溝道效應、亞閾值導通、熱載流子效應等非理想特性至關重要。

- 深度仿真驗證:進行全面的仿真分析,包括:

- 直流工作點分析:確保所有晶體管處于飽和區(或所需的工作區域)。

- 交流小信號分析:獲取頻率響應(增益、帶寬、相位裕度)。

- 瞬態分析:驗證大信號時域響應(建立時間、壓擺率、失真)。

- 噪聲分析:計算輸入參考噪聲,區分熱噪聲與閃爍噪聲(1/f噪聲)。

- 蒙特卡洛分析與工藝角仿真:評估工藝偏差、失配(Mismatch)及溫度變化對電路性能的影響,保證設計的魯棒性。

四、 版圖設計:從電路到物理實現

版圖是將電路圖轉化為可供芯片制造的光刻掩模版的過程,其質量直接決定芯片成敗。

- 匹配性與對稱性:差分對、電流鏡等關鍵模塊需采用共質心、叉指等版圖技術,并添加虛擬器件(Dummy),以最大程度降低工藝梯度與光刻鄰近效應引起的失配。

- 寄生效應控制:精心規劃走線,最小化關鍵路徑(如高阻抗節點)的寄生電阻、電容,尤其是柵極與敏感節點的寄生電容。

- 可靠性設計:遵循設計規則檢查(DRC),進行天線效應預防、閂鎖效應防護(添加保護環)、電遷移檢查以及靜電放電(ESD)保護電路設計。

- 后仿真驗證:提取版圖的寄生參數(RC提取),生成帶寄生信息的網表,進行后仿真。將結果與前仿真對比,確保性能衰減在可接受范圍內。

五、 流片與測試:最終的驗證

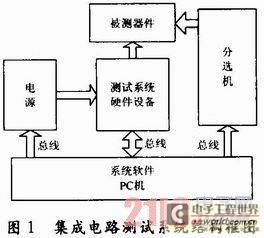

完成版圖并通過電氣規則檢查(ERC)和版圖與電路圖一致性檢查(LVS)后,即可提交給晶圓廠(Foundry)進行流片制造。

- 測試芯片設計:在流片時,通常會在劃片槽或獨立芯片中集成測試結構(如晶體管參數測試單元、環形振蕩器等),用于工藝監控與模型校準。

- 測試方案制定:設計詳細的測試計劃,搭建測試平臺(如PCB、探針臺),使用高精度測試儀器(示波器、頻譜分析儀、網絡分析儀等)對樣片的各項性能指標進行測量,并與設計規格對比。

- 失效分析與迭代:若測試結果不達標,需進行失效分析(可能涉及顯微觀察、探針測試等),定位問題根源(是設計缺陷、模型誤差還是工藝偏差),并在下一次設計迭代中修正。

六、 核心素養與未來趨勢

成為一名優秀的模擬IC設計師,需要深厚的半導體物理基礎、持續的動手實踐以及“如履薄冰”的嚴謹態度。隨著工藝節點持續演進至納米尺度,設計挑戰日益加劇,FinFET等新器件、先進封裝(如Chiplet)、以及模擬與數字混合設計自動化工具的發展,正在重塑模擬IC的設計方法論。

模擬集成電路設計是一條漫長而充滿挑戰的道路,它沒有數字設計那樣高度的自動化,更多地依賴于設計師的經驗、直覺和耐心。這份攻略勾勒了從規格到流片的全景圖,但真正的精通,唯有在無數次的仿真、畫版圖、調試和測試循環中才能獲得。擁抱挑戰,深度思考,您將能設計出在硅片上精確復現構思的卓越電路,讓芯片在現實世界中穩定、高效地運行。

如若轉載,請注明出處:http://m.3tp.com.cn/product/80.html

更新時間:2026-05-08 16:41:31